SN74S373N 供应商

SN74S373N 属性参数

- 标准包装:20

- 类别:集成电路 (IC)

- 家庭:逻辑 - 锁销

- 系列:74S

- 逻辑类型:D 型透明锁存器

- 电路:8:8

- 输出类型:三态

- 电源电压:4.75 V ~ 5.25 V

- 独立电路:1

- 延迟时间 - 传输:7ns

- 输出电流高,低:-

- 工作温度:0°C ~ 70°C

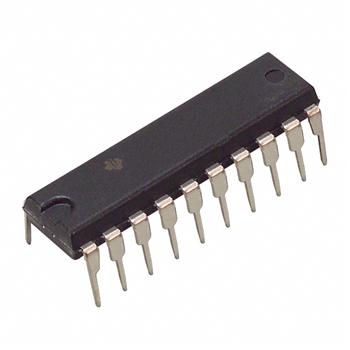

- 安装类型:通孔

- 封装/外壳:20-DIP(0.300",7.62mm)

- 供应商设备封装:20-PDIP

- 包装:管件

- 其它名称:296-34113-5SN74S373N-ND

产品特性

- Choice of Eight Latches or Eight D-Type Flip-Flops in a Single Package

- 3-State Bus-Driving Outputs

- Full Parallel Access for Loading

- Buffered Control Inputs

- Clock-Enable Input Has Hysteresis to Improve Noise Rejection (’S373 and ’S374)

- P-N-P Inputs Reduce DC Loading on Data Lines (’S373 and ’S374)

产品概述

These 8-bit registers feature 3-state outputs

designed specifically for driving highly capacitive

or relatively low-impedance loads. The

high-impedance 3-state and increased

high-logic-level drive provide these registers with

the capability of being connected directly to and

driving the bus lines in a bus-organized system

without need for interface or pullup components.

These devices are particularly attractive for

implementing buffer registers, I/O ports,

bidirectional bus drivers, and working registers.The eight latches of the ’LS373 and ’S373 are transparent D-type latches, meaning that while the enable (C or CLK) input is high, the Q outputs follow the data (D) inputs. When C or CLK is taken low, the output is latched at the level of the data that was set up.The eight flip-flops of the ’LS374 and ’S374 are edge-triggered D-type flip-flops. On the positive transition of the clock, the Q outputs are set to the logic states that were set up at the D inputs.Schmitt-trigger buffered inputs at the enable/clock lines of the ’S373 and ’S374 devices simplify system design as ac and dc noise rejection is improved by typically 400 mV due to the input hysteresis. A buffered output-control (OC) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly.OC\ does not affect the internal operation of the latches or flip-flops. That is, the old data can be retained or new data can be entered, even while the outputs are off.