SN74LS293N 供应商

-

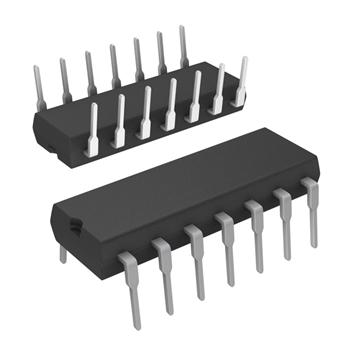

SN74LS293N

品牌:TI 封装/批号:原厂原装/22+ -

SN74LS293N

品牌: 封装/批号:DIP/2019+ -

SN74LS293N

品牌:TI 封装/批号:DIP14/新年份 -

SN74LS293N

品牌:TI 封装/批号:TSSOP/23+ -

SN74LS293NG4

品牌:TI(德州仪器) 封装/批号:PDIP-14/2022+

SN74LS293N 属性参数

- 标准包装:25

- 类别:集成电路 (IC)

- 家庭:逻辑 -计数器,除法器

- 系列:74LS

- 逻辑类型:二进制计数器

- 方向:上

- 元件数:1

- 每个元件的位元数:4

- 复位:同步

- 计时:-

- 计数速率:42MHz

- 触发器类型:正边沿

- 电源电压:4.75 V ~ 5.25 V

- 工作温度:0°C ~ 70°C

- 安装类型:通孔

- 封装/外壳:14-DIP(0.300",7.62mm)

- 供应商设备封装:14-PDIP

- 包装:管件

- 其它名称:296-33989-5SN74LS293N-ND

产品特性

- GND and VCC on Corner Pins (Pins 7 and 14 Respectively)

产品概述

The SN54290/SN74290, SN54LS290/SN74LS290, SN54293/SN74293, and SN54LS293/SN74LS293

counters are electrically and functionally identical to the SN5490A/SN7490A,

SN54LS90/SN74LS90, SN5493A/SN7493A, and SN54LS93/SN74LS93, respectively. Only

the arrangement of the terminals has been changed for the '290, 'LS290, '293,

and 'LS293.

Each of these monolithic counters contains four master-slave flip-flops

and additional gating to provide a divide-by-two counter and a three-stage

binary counter for which the count cycle length is divide-by-five for the

'290 and 'LS290 and divide-by-eight for the '293 and 'LS293.

All of these counters have a gated zero reset and the '290 and 'LS290 also

have gated set-to-nine inputs for use in BCD nine's complement applications.

To use the maximum count length (decade or four-bit binary) of these counters,

the B input is connected to the QA output. The input count pulses

are applied to input A and the outputs are as described in the appropriate

function table. A symmetrical divide-by-ten count can be obtained from the

'290 and 'LS290 counters by connecting the QD output to the A input

and applying the input count to the B input which gives a divide-by-ten square

wave at output QA.